#### AIM OF THE EXPERIMENT:

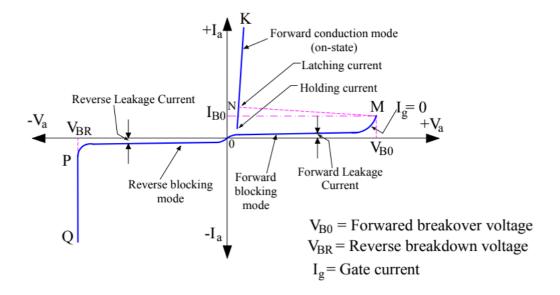

To study and plot V-I characteristics of SCR.

# **APPARATUS REQUIRED:**

| SL No. | Name of Apparatus | Specification | Quantity |

|--------|-------------------|---------------|----------|

| 1      | SCR Trainer       |               |          |

| 2      | Mains supply      |               |          |

| 3      | DC power supply   |               |          |

| 4      | Voltmeter         |               |          |

| 5      | Ammeter           |               |          |

| 6      | Patch cords       |               |          |

#### **THEORY**

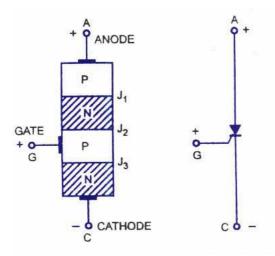

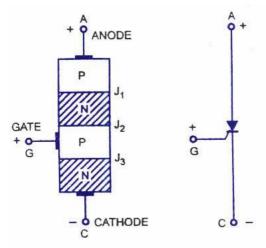

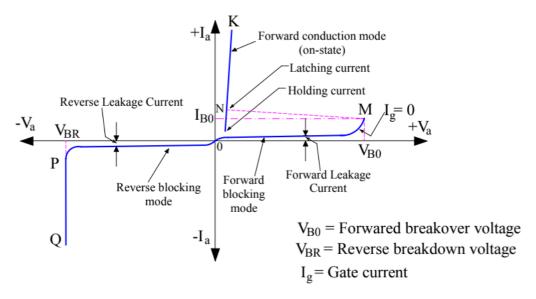

A thyristor is a four-layer semiconductor device of PNPN structure with three PN junctions. It has three terminal anode, cathode and gate. When the anode voltage is made positive with respect to cathode, the junctions Ji and J are forward biased. The junctions Ji is reversed biased and, only a small leakage current flows from anode to cathode. The thyristor is then said to be in the OFF mode. If a Anode to Cathode voltage is increased to a sufficiently large value, the reversed biased junction Ji will break. This is known as avalanche breakdown and the corresponding voltage is called forward breakdown voltage VBO. Since junctions  $J_1$  and  $J_3$  are already forward biased, there will be free movement of carriers across all three junctions, resulting in a large forward anode current. The device will then be in a conducting state or on state. The voltage drop would be due to the ohmic drop in the four layers and it is small, typically, 1V. In the on state, the anode current is limited by an external impedance or resistance.

## **MODEL GRAPH**

## **CIRCUIT DIAGRAM**

## **PROCEDURE**

- 1. Connections were made as per the circuit diagram.

- 2. Initially VG & VA were kept at minimum position and R 1 & R2 at maximum position.

- 3. The Gate current lg was adjusted to some constant by varying the VG or RG.

- 4. VA is slowly varied and the anode to cathode voltage VAK and Anode current IA was observed.

- 5. The above procedure was repeated for different Gate current lg.

## **OBSERVATION TABLE**

| SL. No. | Anode voltage (VAK in volt) | Anode current (IA in mA) |

|---------|-----------------------------|--------------------------|

|         |                             |                          |

|         |                             |                          |

|         |                             |                          |

|         |                             |                          |

|         |                             |                          |

|         |                             |                          |

| CONCLUSION | CON | CLU | JSI | ON |

|------------|-----|-----|-----|----|

|------------|-----|-----|-----|----|

Sign. of the Student

Sign. of the faculty

#### AIM OF THE EXPERIMENT

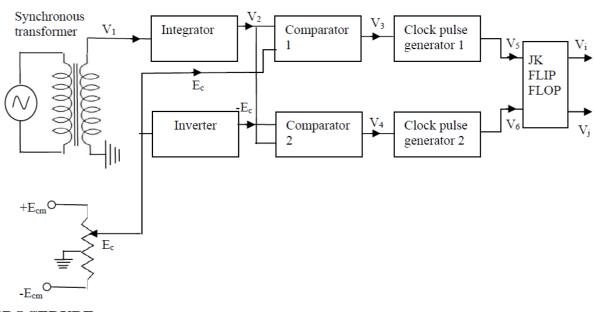

To study the cosine-controlled triggering circuit

#### APPARATUS REQUIRED

| SL No. | Name of Apparatus  | Specification | Quantity |

|--------|--------------------|---------------|----------|

| 1      | Cosine Trainer Kit |               |          |

| 2      | Mains supply       |               |          |

| 3      | DC power supply    |               |          |

| 4      | Multimeter         |               |          |

| 5      | Ammeter            |               |          |

| 6      | DSO                |               |          |

| 7      | Patch cords        |               |          |

#### **THEORY**

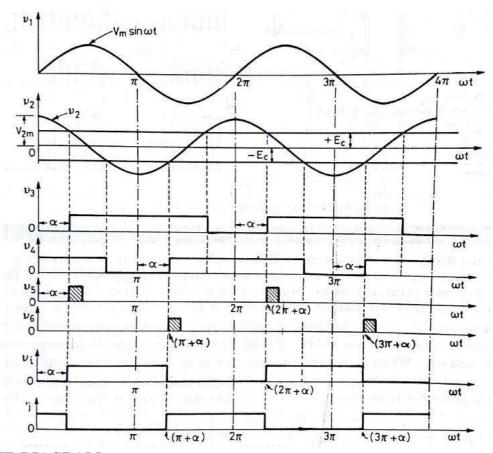

The synchronizing transformer steps down the supply voltage to an appropriate level. The input to this transformer is taken from the same source from which converter circuit is energized. The output voltage  $V_1$  of synchronizing transformer is integrated to get cosine-wave  $V_2$ . The dc. control voltage  $E_e$  varies from maximum positive  $E_{cm}$  to maximum negative  $E_{cm}$  so that firing angle can be varied from zero to  $180^\circ$ . The cosine wave  $V_2$  is compared in comparators 1 and 2 with  $E_e$  and  $E_e$ . When  $E_e$  is high as compared to  $E_e$ 0 output voltage  $E_e$ 1 is available from comparator-1. Same is true for comparator-2. So, the comparators 1 and 2 give output pulses  $E_e$ 1 and  $E_e$ 2 is high as shown in the Fig. It is seen from this figure that firing angle is governed by the intersection of  $E_e$ 2 and  $E_e$ 3. When  $E_e$ 4 is maximum, firing angle is zero. Thus, firing angle  $E_e$ 3 in terms of  $E_e$ 4 and  $E_e$ 5 can be expressed as

$$V_{2cm}\cos\alpha = E_c$$

$$\alpha = \cos^{-1} \left( \frac{E_c}{V_{2cm}} \right)$$

The signals  $V_3$ ,  $V_4$  obtained from comparators are fed to clock-pulse generators 1, 2 to get clock pulses  $V_s$ ,  $V_G$  as shown in Fig. These signals  $V_s$ ,  $V_G$  energies a JK flip flop to generate output signals  $V_i$  and  $V_j$ . The signal  $V_j$  is amplified through the circuit and is then employed to turn on the SCRs in the positive half cycle. Signal  $V_j$ , after amplification. is used to trigger SCRs in the negative half cycle.

For a single-phase full converter, average output voltage is given by

$$V_0 = \frac{2V_m}{\pi} \cos \alpha$$

$$V_0 = \frac{2V_m}{\pi} \cos \left( \cos^{-1} \left( \frac{E_c}{V_{2cm}} \right) \right)$$

$$V_0 = kE_c$$

This shows that cosine firing scheme provides a linear transfer characteristic between the average output voltage Vo and the control voltage Ee. This scheme, on account of its linear transfer characteristic, improves the closed-loop response of the converter system.

# **MODEL GRAPH**

# **CIRCUIT DIAGRAM**

# **PROCEDURE**

- 1. The power supply was switched on.

- 2. The DSO was switched on.

- 3. The pulse realise switch  $S_1$  was switched on.

- 4. The peak value of AC input voltage  $E_{\text{m}}$  and trigger angle  $\alpha$  was noted down.

- 5. The Output voltage  $V_0$  and corresponding firing angle  $\alpha$  was observed by varying the pot  $P_{1.}$

# **OBSERVATION TABLE**

| Sl. No. | Trigger Angle (α) | Output voltage |

|---------|-------------------|----------------|

|         |                   |                |

|         |                   |                |

|         |                   |                |

|         |                   |                |

|         |                   |                |

| OON. | TICIT        | ON     |

|------|--------------|--------|

| CON  | $\mathbf{U}$ | $\cup$ |

Sign. of the Student

Sign. of the faculty

## AIM OF THE EXPERIMENT

To measure the latching and holding current of SCR.

# APPARATUS REQUIRED

| SL No. | Name of Apparatus | Specification | Quantity |

|--------|-------------------|---------------|----------|

| 1      | SCR Trainer       |               |          |

| 2      | Mains supply      |               |          |

| 3      | DC power supply   |               |          |

| 4      | Voltmeter         |               |          |

| 5      | Ammeter           |               |          |

| 6      | Patch cords       |               |          |

## **THEORY**

A thyristor is a four-layer semiconductor device of PNPN structure with three PN junctions. It has three terminal anode, cathode and gate. When the anode voltage is made positive with respect to cathode, the junctions  $J_1$  and  $J_3$  are forward biased. The junctions  $J_2$  is reversed biased and, only a small leakage current flows from anode to cathode. The thyristor is then said to be in the OFF mode. If a Anode to Cathode voltage is increased to a sufficiently large value, the reversed biased junction  $J_2$  will break. This is known as avalanche breakdown and the corresponding voltage is called forward breakdown voltage  $V_{Bo}$ . Since junctions  $J_1$  and  $J_3$  are already forward biased, there will be free movement of carriers across all three junctions, resulting in a large forward anode current. The device will then be in a conducting state or on state. The voltage drop would be due to the ohmic drop in the four layers and it is small, typically, IV. In the on state, the anode current is limited by an external impedance or resistance.

#### **CIRCUIT DIAGRAM**

## **PROCEDURE**

## To find latching current:

- 1. R1 was kept at middle position.

- 2. By varying V<sub>2</sub> 20V was applied to the Anode to cathode.

- 3. The  $V_g$  voltage was increased by varying  $V_a$  till the device turns ON indicated by sudden rise in  $I_A$ .

- 4. Now R<sub>A</sub> was set at maximum position, then SCR turns OFF.

- 5. Now the R<sub>A</sub> was decreased slowly, to increase the Anode current gradually in steps.

- 6. At each and every step, the gate was made OFF and ON, voltage switches Va. If the Anode current is greater than the latching current of the device, the device says ON even after switch S<sub>1</sub>OFF, otherwise device goes to blocking mode as soon as the gate switch is put OFF.

- 7. If I<sub>A</sub>>I<sub>L</sub> then, the device remains in ON state that anode current as latching current was recorded.

#### To find holding current:

- 1. The load current was increased from latching current level by varying R<sub>A</sub> & V<sub>A</sub>.

- 2. The gate voltage switch  $S_1$  was made off permanently (now the device is in ON state).

- 3. The load resistance(R2) was increased, so that anode current started reducing, at some anode current the device goes to turn off which was noted down. Take small steps to get accurate holding current value.

| the faculty |

|-------------|

|             |

## **EXPERIMENT: -4(a)**

## AIM OF THE EXPERIMENT

To study the single-phase half wave-controlled rectifier with R and R-L load.

## **APPARATUS REQUIRED**

| SLNo. | Name of Apparatus                        | Specification | Quantity |

|-------|------------------------------------------|---------------|----------|

| 1     | 1-phase controlled rectifier trainer kit |               |          |

| 2     | Gate triggering circuit                  |               |          |

| 3     | DSO                                      |               |          |

| 4     | 1-ph Variac                              |               |          |

| 5     | Multi-meter                              |               |          |

| 6     | R and R-L load                           |               |          |

| 7     | Connecting wires                         |               |          |

#### **THEORY**

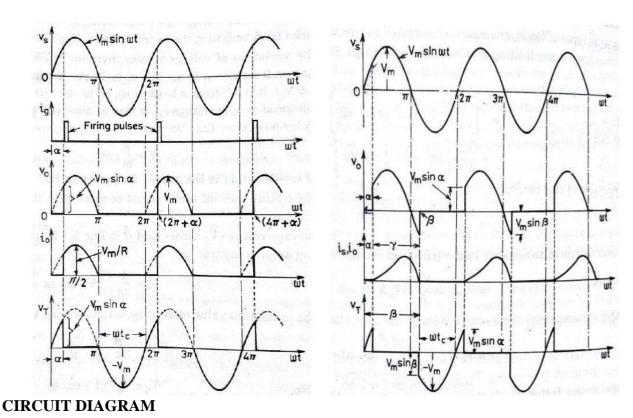

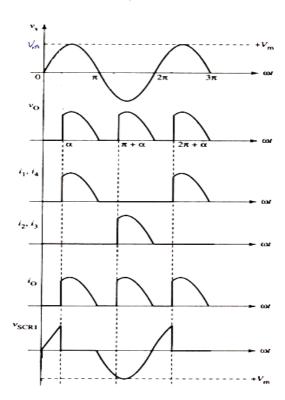

We know that thyristor is a unidirectional device, allowing the flow of current only in one direction. When the thyristor is forward-biased i.e., anode terminal is positive with respect to the cathode terminal, and the gate terminal is not triggered, there will be no conduction due to the reverse biasing of the inner junction of SCR. Hence, the entire supply voltage appears across the SCR. The magnitude of the conduction current depends upon the instant when it is triggered i.e., firing angle ' $\alpha$ ', and the load resistance R. Since the circuit does not contain any energy storing elements, the load current will be in phase with voltage and becomes zero instantaneously with the voltage at zero crossing (at  $\omega t = \pi$  rad/sec). The load current and voltage are zero from 0 to  $\alpha$ . When SCR is triggered by giving gate signal at  $\alpha$ . The entire supply voltage except for drop across SCR will be applied across the load (from  $\omega t = \alpha$  to  $\omega t = \pi$ ). At  $\omega t = \pi$ , the phase reversal takes place and the negative half-cycle of the input supply will start. Due to the negative half-cycle, the SCR will be reverse biased and will be turned OFF at  $\omega t = \pi$ . From  $\omega t = \pi$  to  $\omega t = 2\pi$ , the load current and voltage will be zero. Again, when the positive half cycle starts i.e., from  $\omega t = 2\pi$ , SCR will be forward biased but it will not be switched ON until it is triggered i.e., until  $\omega t = (2\pi + \alpha)$

# **MODEL GRAPH**

# **PROCEDURE**

- 1. The Connections were made as per the circuit diagram.

- 2. The CRO and voltmeter was connected across the load.

- 3. The potentiometer was kept at the minimum position.

- 4. AC source was switched on.

- 5. The output wave form was observed and the output voltage was calculated.

# **OBSERVATION TABLE**

| Sl. No. | Firing angle (a) | I/P<br>Voltage<br>(Volts) | O/P<br>Voltage<br>(Volts) |

|---------|------------------|---------------------------|---------------------------|

|         |                  |                           |                           |

|         |                  |                           |                           |

| TRACINGS             |                      |

|----------------------|----------------------|

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

| CONCLUSION           |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

| Sign. of the Student | Sign. of the faculty |

| sign. of the student | Sign. of the faculty |

|                      |                      |

|                      |                      |

|                      |                      |

|                      |                      |

# **EXPERIMENT: -4(b)**

## AIM OF THE EXPERIMENT

To study the single-phase half wave semi-controlled rectifier with R and R-L load.

# APPARATUS REQUIRED

| Sl. No. | Name of Apparatus       | Specification | Quantity |

|---------|-------------------------|---------------|----------|

| 1       | I-phase SCR controlled  |               |          |

|         | trainer kit             |               |          |

| 2       | Gate triggering circuit |               |          |

| 3       | DSO                     |               |          |

| 4       | 1-ph Variac             |               |          |

| 5       | Multi-meter             |               |          |

| 6       | R, R-L, Lamp Load       |               |          |

| 7       | Connecting wires        |               |          |

#### **THEORY**

The bridge circuit of the semi converter has two diodes  $(D_1, D_2)$  and two SCRs  $(T_1, T_2)$ . Pair of a diode and SCR  $(D_2, T_1)$  is connected in the parallel with another pair of a diode and SCR  $(D_1, T_2)$ . And finally, the bridge circuit has a parallel connection with the RL circuit. Thus, this bridge circuit is the main circuit of the semi converter.

## **MODEL GRAPH**

**CIRCUIT DIAGRAM**

# **PROCEDURE**

- 1. The Connections were made as per the circuit diagram.

- 2. The voltmeter and DSO was connected across the load.

- 3. The potentiometer was kept at the minimum position.

- 4. AC source was switched on.

- 5. The output wave form was observed and the output voltage was calculated.

# **OBSERVATION TABLE**

| Sl. No. | Firing angle (α) | I/P<br>Voltage<br>(Volts) | O/P<br>Voltage<br>(Volts) |

|---------|------------------|---------------------------|---------------------------|

|         |                  |                           |                           |

|         |                  |                           |                           |

|         |                  |                           |                           |

|         |                  |                           |                           |

# **TRACINGS**

#### AIM OF THE EXPERIMENT

To study single-phase full wave-controlled rectifier circuits (Bridge type) with R-load.

# APPARATUS REQUIRED

| SL.No. | Name of Apparatus       | Specification | Quantity |

|--------|-------------------------|---------------|----------|

| 1      | SCR trainer kit         |               |          |

| 2      | Gate triggering circuit |               |          |

| 3      | DSO                     |               |          |

| 4      | 1-ph Variac             |               |          |

| 5      | Multi-meter             |               |          |

| 6      | Ammeter                 |               |          |

| 7      | Connecting wires        |               |          |

#### **THEORY**

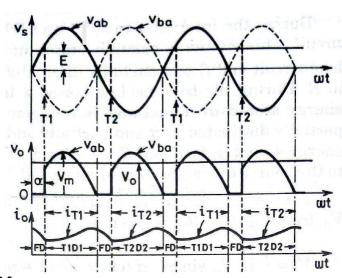

A fully controlled converter uses thyristors only and there is a wider control over the de output voltage. With pure resistive load, it is single quadrant converter. Here, both the output voltage and output current are positive. With the RL-load it becomes a two-quadrant converter. Here, output voltage is either positive or negative but output current is always positive. This type of full wave rectifier circuit consists of four SCRs.

During the positive half cycle, SCRs  $T_1$  and  $T_2$  are forward biased. At  $\omega t = \alpha$ , SCRs  $T_1$  and  $T_2$  are triggered, then the current flows through the AC+ -  $T_1$ -R load -  $T_2$ -AC-. At  $\omega t = \pi$ , supply voltage falls to zero and the current also goes to zero. Hence SCRs  $T_1$  and  $T_2$  turned off. During negative half cycle ( $\pi$  to  $2\pi$ ). SCRs  $T_3$  and  $T_4$  are forward biased. At  $\omega t = \pi + \alpha$ , SCRs  $T_3$  and  $T_4$  are triggered, then current flows through the path AC+ -  $T_3$ -R load -  $T_4$ -AC-. At  $\omega t = 2\pi$ , the supply voltage and current go to zero, SCRs  $T_3$  and  $T_4$  are turned off. The output voltage is given by

$$V_0 = \frac{V_m}{\pi} \left( 1 + \cos \alpha \right)$$

## **MODEL GRAPH**

# **CIRCUIT DIAGRAM**

# **PROCEDURE**

- 1. The Connections were made as per the circuit diagram.

- 2. The voltmeter and DSO was connected across the load.

- 3. The potentiometer was kept at the minimum position.

- 4. AC source was switched on.

- 5. The output wave form was observed and the output voltage was calculated.

# **OBSERVATION TABLE**

| Sl. No. | Firing angle | I/P                | O/P                |

|---------|--------------|--------------------|--------------------|

|         | (α)          | Voltage<br>(Volts) | Voltage<br>(Volts) |

|         |              |                    |                    |

|         |              |                    |                    |

|         |              |                    |                    |

|         |              |                    |                    |

## **TRACINGS**

#### AIM OF THE EXPERIMENT

To study Three Phase Semi-controlled & Fully Controlled Rectifier circuit with R load.

# APPARATUS REQUIRED

| SL No. | Name of Apparatus             | Specification | Quantity |

|--------|-------------------------------|---------------|----------|

| 01     | 3-phase Power modulator Kit   |               |          |

| 02     | DSO                           |               |          |

| 03     | Ammeter, Voltmeter            |               |          |

| 04     | 3-phase Variac                |               |          |

| 05     | Multi-meter                   |               |          |

| 06     | Patch Chord/ Connecting leads |               |          |

## **THEORY**

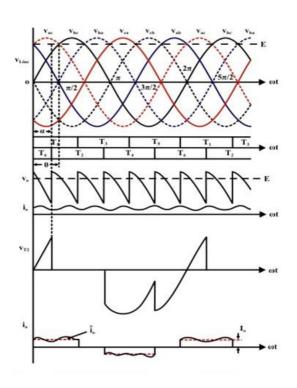

For any current to flow in the load at least one device from the top group  $(T_1, T_3, T_5)$  and one from the bottom group  $(T_2, T_4, T_6)$  must conduct. Then from symmetry consideration it can be argued that each thyristor conducts for  $120^\circ$  of the input cycle. Now the thyristors are fired in the sequence  $T_1 \to T_2 \to T_3 \to T_4 \to T_5 \to T_6 \to T_1$  with  $60^\circ$  interval between each firing. Therefore, thyristors on the same phase leg are fired at an interval of  $180^\circ$  and hence cannot conduct simultaneously. This leaves only six possible conduction mode for the converter in the continuous conduction mode of operation. These are  $T_1T_2, T_2T_3, T_3T_4, T_4T_5, T_5T_6, T_6T_1$ . The output voltage is given by

$$V_0 = \frac{3\sqrt{2}}{\pi} V_L cos\alpha$$

#### **MODEL GRAPH**

# **CIRCUIT DIAGRAM**

# **PROCEDURE**

- 1. The Connections were made as per the circuit diagram.

- 2. The voltmeter and DSO was connected across the load.

- 3. The potentiometer was kept at the minimum position.

- 4. AC source was switched on.

- 5. The output wave form was observed and the output voltage was calculated.

# **OBSERVATION TABLE**

| Sl. No. | Firing angle (α) | I/P<br>Voltage<br>(Volts) | O/P<br>Voltage<br>(Volts) |

|---------|------------------|---------------------------|---------------------------|

|         |                  |                           | , ,                       |

|         |                  |                           |                           |

|         |                  |                           | _                         |

|         |                  |                           |                           |

## **TRACINGS**

## AIM OF THE EXPERIMENT

To study of single Phase PWM Voltage Source Inverter.

# APPARATUS REQUIRED

| SL No. | Name of Apparatus   | Specification | Quantity |

|--------|---------------------|---------------|----------|

| 01     | Power modulator Kit |               |          |

| 02     | DSO                 |               |          |

| 03     | Ammeter/Voltmeter   |               |          |

| 04     | Load                |               |          |

| 05     | Connecting Leads    |               |          |

#### **THEORY**

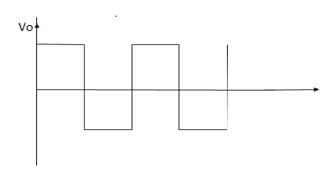

The system consists of two independent circuits illustrating single-phase PWM voltage- sourced inverters. The Half-Bridge Converter block and the Full-Bridge converter block are modeling simplified model of an IGBT/Diode pair where the forward voltages of the forced- commutated device and diode are ignored. The converters are controlled in open loop with the PWM Generator blocks. The two circuits use the same DC voltage, carrier frequency and modulation index. Switches shown in the circuit diagrams are power electronics switches. For low voltage and low power applications power BJTs are used, for medium power applications power MOSFETs & power IGBTs are used and for high voltage and high-power applications power IGCTs are used.

#### **MODEL GRAPH**

**CIRCUIT DIAGRAM**

# **PROCEDURE**

- 1. The Connections were made as per the circuit diagram.

- 2. The voltmeter and DSO was connected across the load.

- 3. The output wave form was observed and the output voltage was calculated.

- 4. The carrier frequency was varied to obtain different values of output voltage and current.

# **OBSERVATION TABLE**

| Sl. No. | Frequency | O/P        | O/P     |

|---------|-----------|------------|---------|

|         |           | Current(A) | Voltage |

|         |           |            | (Volts) |

|         |           |            |         |

|         |           |            |         |

|         |           |            |         |

|         |           |            |         |

|    |   | ~-   |   | _   | _ |

|----|---|------|---|-----|---|

| TR | Δ | ( II | N | יבו | Ľ |

#### AIM OF THE EXPERIMENT

To study of the fly back converter and forward converter.

# APPARATUS REQUIRED

| SL No. | Name of Apparatus          | Specification | Quantity |

|--------|----------------------------|---------------|----------|

| 1      | MOSFET based Forward &     |               |          |

|        | Flyback Converter kit      |               |          |

| 2      | DC Regulated Power supply- |               |          |

|        | 0-30V/2A (single)          |               |          |

| 3      | Rheostat- I 00 ohms/2Amps. |               |          |

| 4      | CRO                        |               |          |

| 5      | Patch cords                |               |          |

#### **THEORY**

## Fly Back Converter:

A flyback converter is a very practical isolated version of the buck-boost converter. The inductor of the buck-boost converter has been replaced by a flyback transformer. The input dc source Vs and switch S are connected in series with the transformer primary. The diode D and the RC output circuit are connected in series with the secondary of the flyback transformer. When the switch S is on, the current in the magnetizing inductance increases linearly, the diode D is off and there is no current in the ideal transformer windings. When the switch is turned off, the magnetizing inductance current is diverted into the ideal transformer, the diode turns on, and the transformed magnetizing inductance current is supplied to the R-C load. The output voltage is given by

$$V_0 = V_S \times \frac{N_2}{N_1} \times \frac{D}{1 - D}$$

#### Forward Converter:

When the switch S is on, diode  $D_1$  conducts and diode  $D_2$  is off. The energy is transferred from the input, through the transformer, to the output filter. When the switch S is off, the state of diodes  $D_1$  and  $D_2$  is reversed. In the forward converter, the energy-transfer current flows through the transformer in one direction. Hence, an additional winding with diode  $D_3$  is needed to bring the magnetizing current of the transformer to zero, which prevents transformer saturation. The turns ratio  $N_1$ = $N_3$  should be selected in such a way that the magnetizing current decreases to zero during a fraction of the time interval when the switch S is off. The output voltage is given by

$$V_0 = V_S \times \frac{N_2}{N_1} \times D$$

#### **CIRCUIT DIAGRAM**

|               | onnections were made as particular and DSO was conn |                |                                |

|---------------|-----------------------------------------------------|----------------|--------------------------------|

| 3. The out    | put voltage was recorded.                           |                |                                |

| <b>DBSERV</b> | ATION TABLE                                         |                |                                |

| For flybacl   | k Converter:                                        |                |                                |

| SL. NO.       | I/P Voltage (Vs)                                    | Duty Cycle (%) | Load Voltage (V <sub>0</sub> ) |

|               |                                                     |                |                                |

|               |                                                     |                |                                |

|               |                                                     |                |                                |

| For forwar    | d Converter:                                        |                |                                |

| SL. NO.       | I/P Voltage (V <sub>S</sub> )                       | Duty Cycle (%) | Load Voltage (V <sub>0</sub> ) |

|               |                                                     |                |                                |

|               |                                                     |                |                                |

|               |                                                     |                |                                |